The University of Texas at Austin

The University of Texas at AustinHi all! I am a Ph.D. student in Computer Science (CS) at the University of Texas at Austin, working with Prof. Keshav Pingali. I received my B.S. degree in Electrical Engineering and Computer Science (EECS) from Seoul National University with highest honor, in 2023. My research interest is in Reinforcement Learning and Large-scale Distributed Systems.

Action required

Problem: The current root path of this site is "baseurl ("_config.yml.

Solution: Please set the

baseurl in _config.yml to "Education

-

The University of Texas at AustinPh.D. in Computer Science (CS)Sep. 2025 - Current

The University of Texas at AustinPh.D. in Computer Science (CS)Sep. 2025 - Current -

The University of Texas at AustinPh.D. in Electrical and Computer Engineering (ECE)Sep. 2024 - Aug. 2025

The University of Texas at AustinPh.D. in Electrical and Computer Engineering (ECE)Sep. 2024 - Aug. 2025 -

Seoul National UniversityB.S. in Electrical Engineering and Computer Science (EECS)Mar. 2017 - Oct. 2023

Seoul National UniversityB.S. in Electrical Engineering and Computer Science (EECS)Mar. 2017 - Oct. 2023

Honors & Awards

-

DAC Young Fellowship, 62nd Design Automation Conference (DAC)Jun. 2025

-

UT Excellence Engineering Fellowship, UT AustinSep. 2024

-

Golden Tiger Award, USAG HumphreysDec. 2019

Selected Publications (view all )

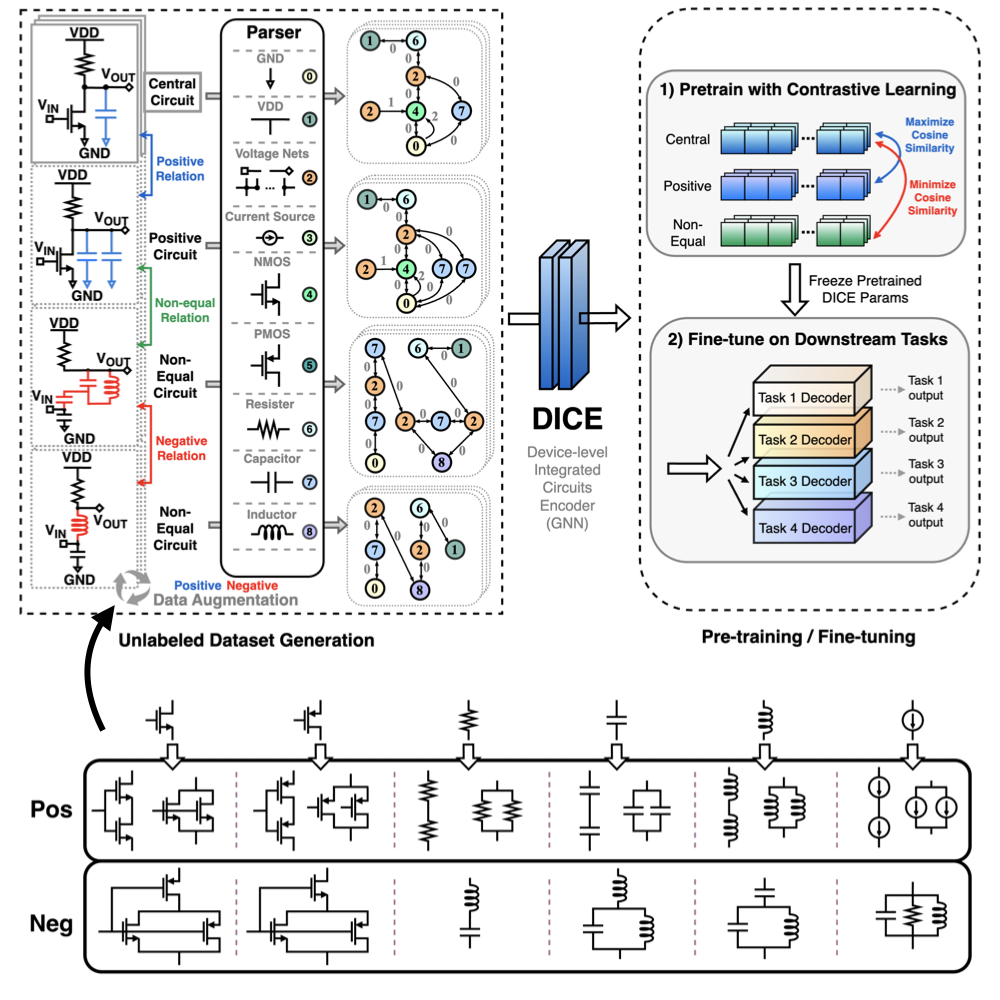

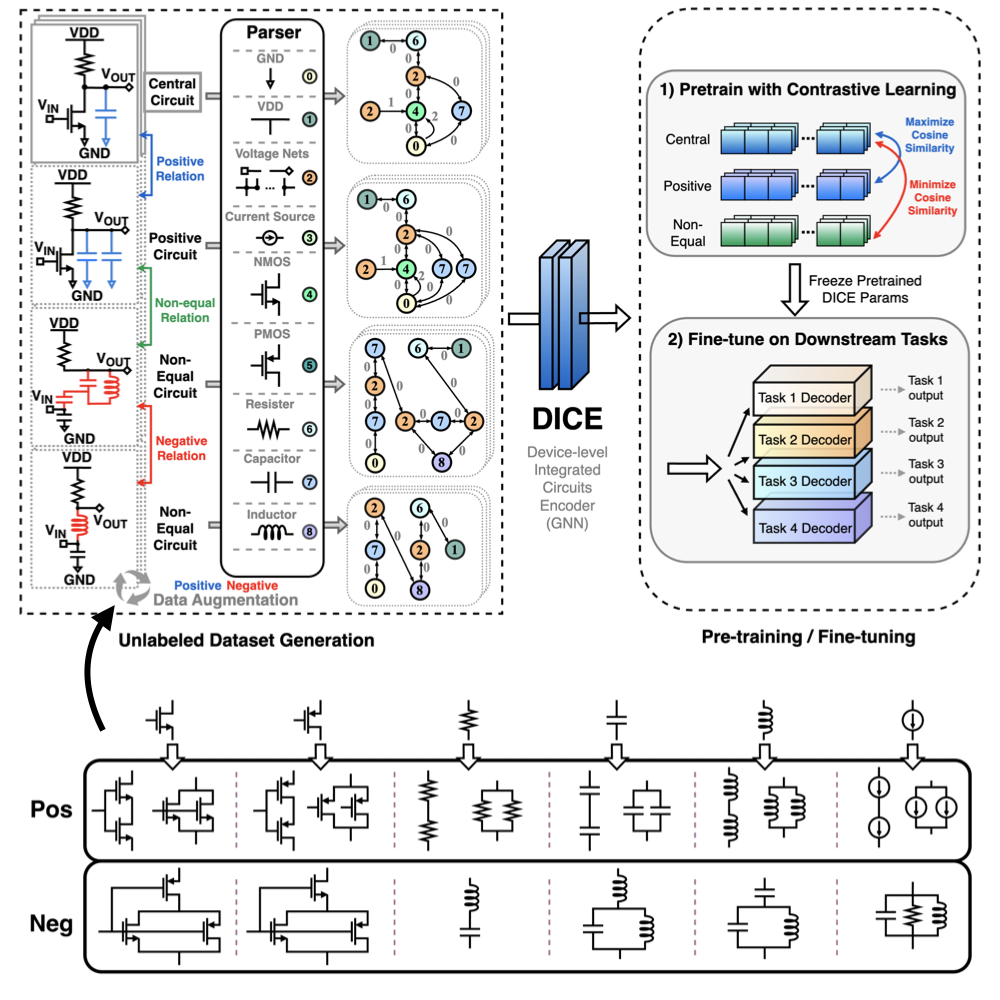

DICE: Device-level Integrated Circuits Encoder with Graph Contrastive Pretraining

Sungyoung Lee, Ziyi Wang, Seunggeun Kim, Taekyun Lee, Yao Lai, David Z. Pan

arXiv 2025

DICE is the first self-supervised pretrained GNN for device-level circuit representation, covering both analog and digital circuits. DICE is pretrained with simulation-free graph contrastive learning, leading to substantial performance gain in three downstream tasks.

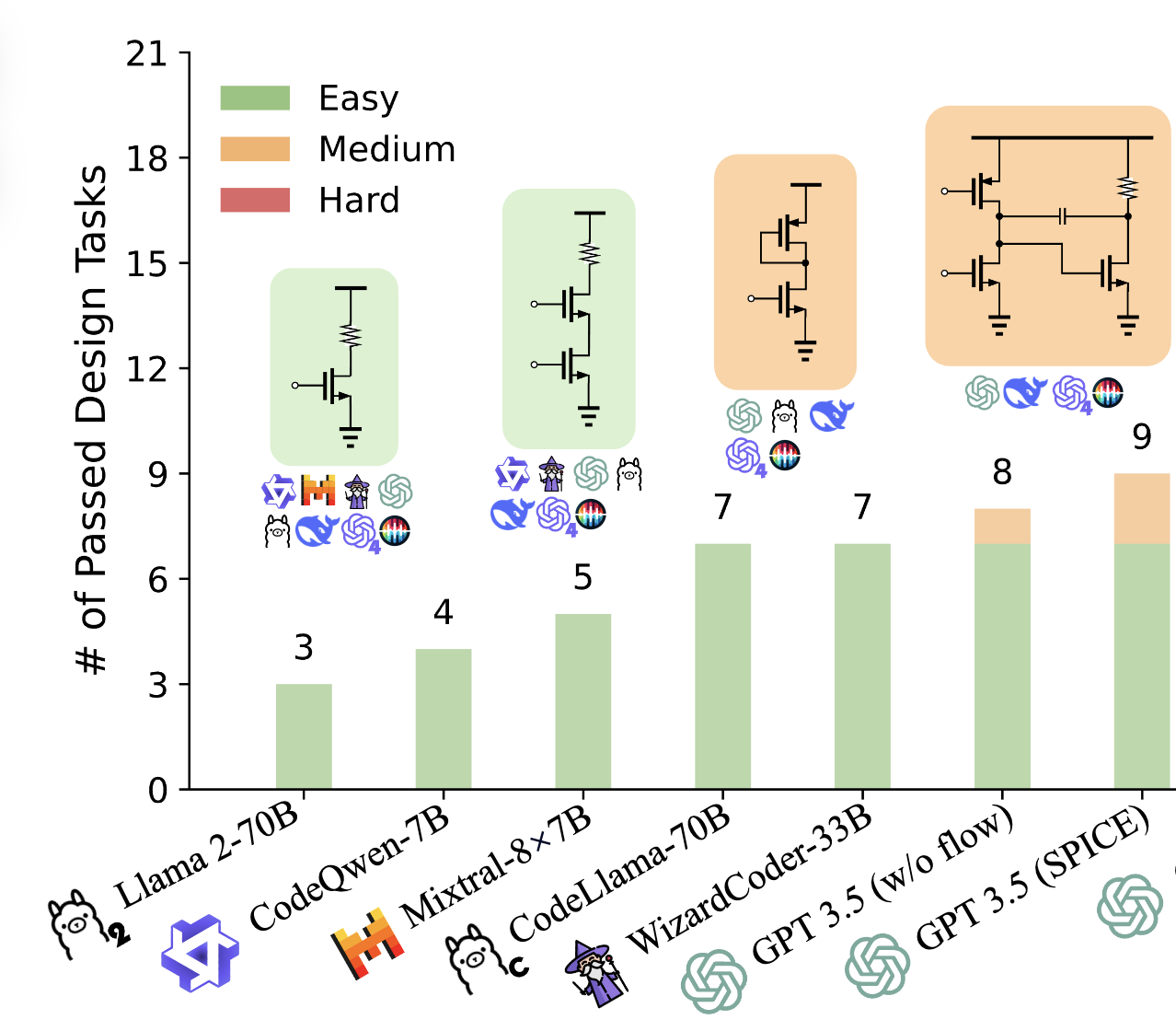

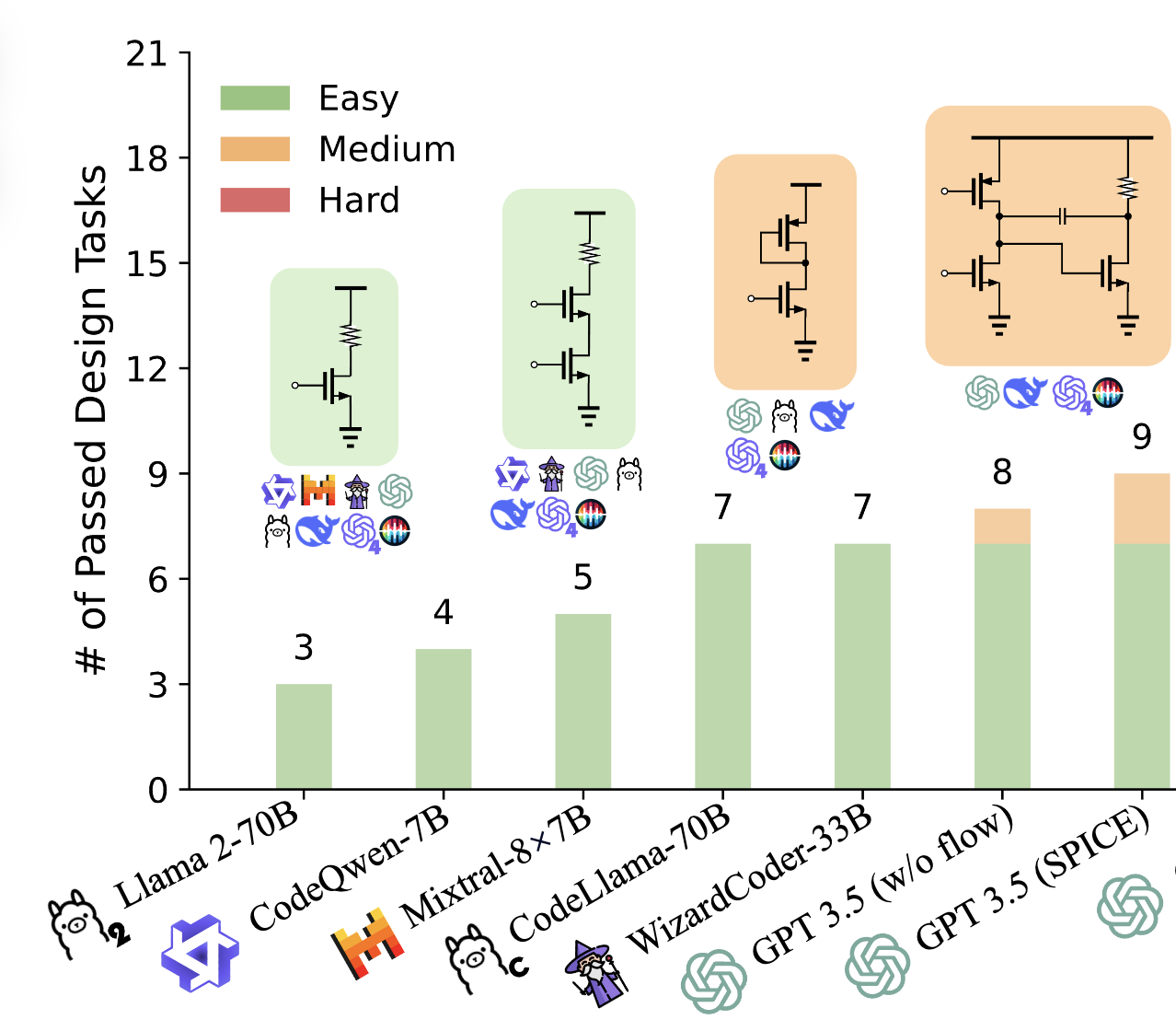

AnalogCoder: Analog Circuit Design via Training-Free Code Generation

Yao Lai, Sungyoung Lee, Guojin Chen, Souradip Poddar, Mengkang Hu, David Z. Pan, Ping Luo

AAAI Conference on Artificial Intelligence (AAAI) 2025 Oral

AnalogCoder is a training-free LLM agent for analog circuit design, using feedback-driven prompts and a circuit library to achieve high success rates, outperforming GPT-4o by designing 25 circuits.

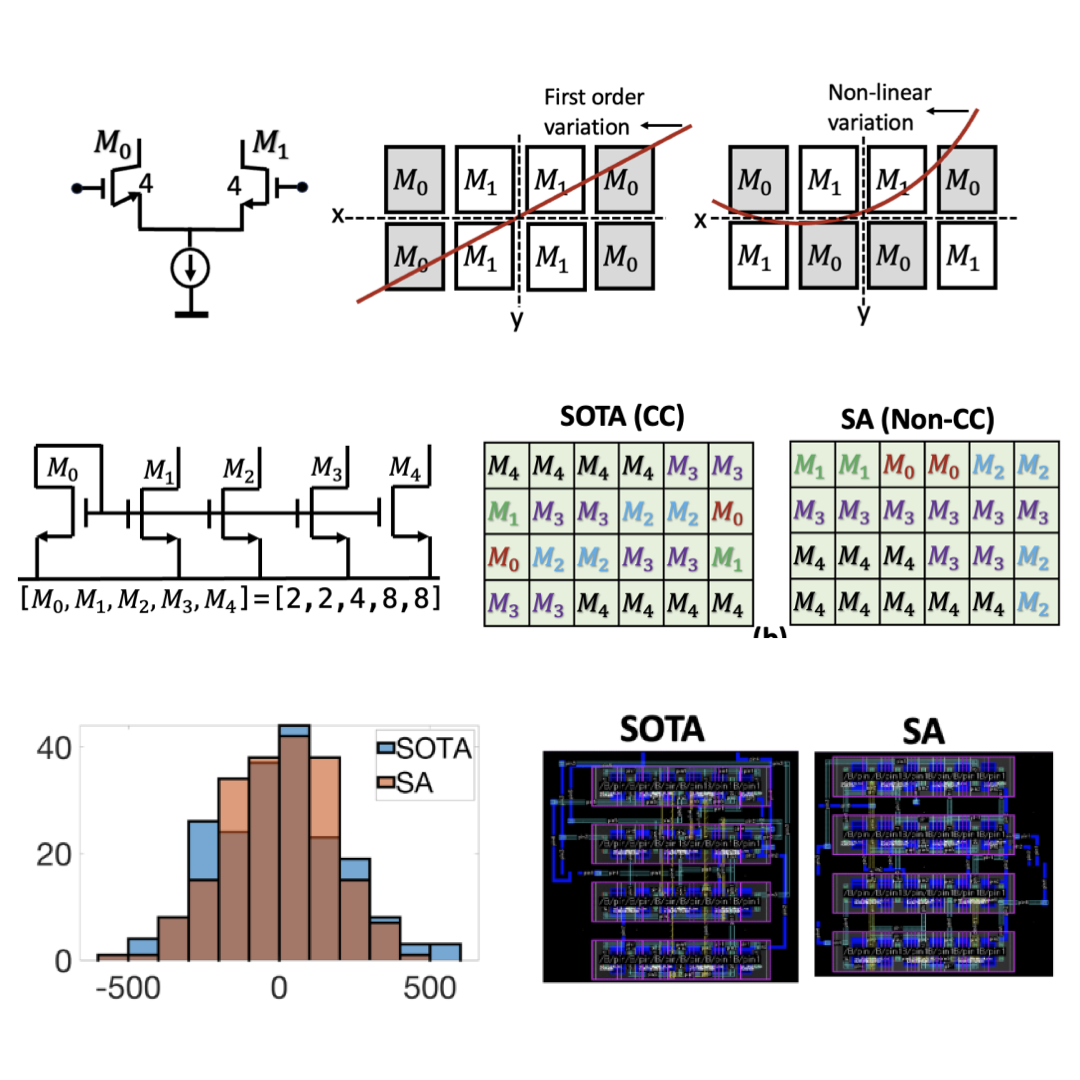

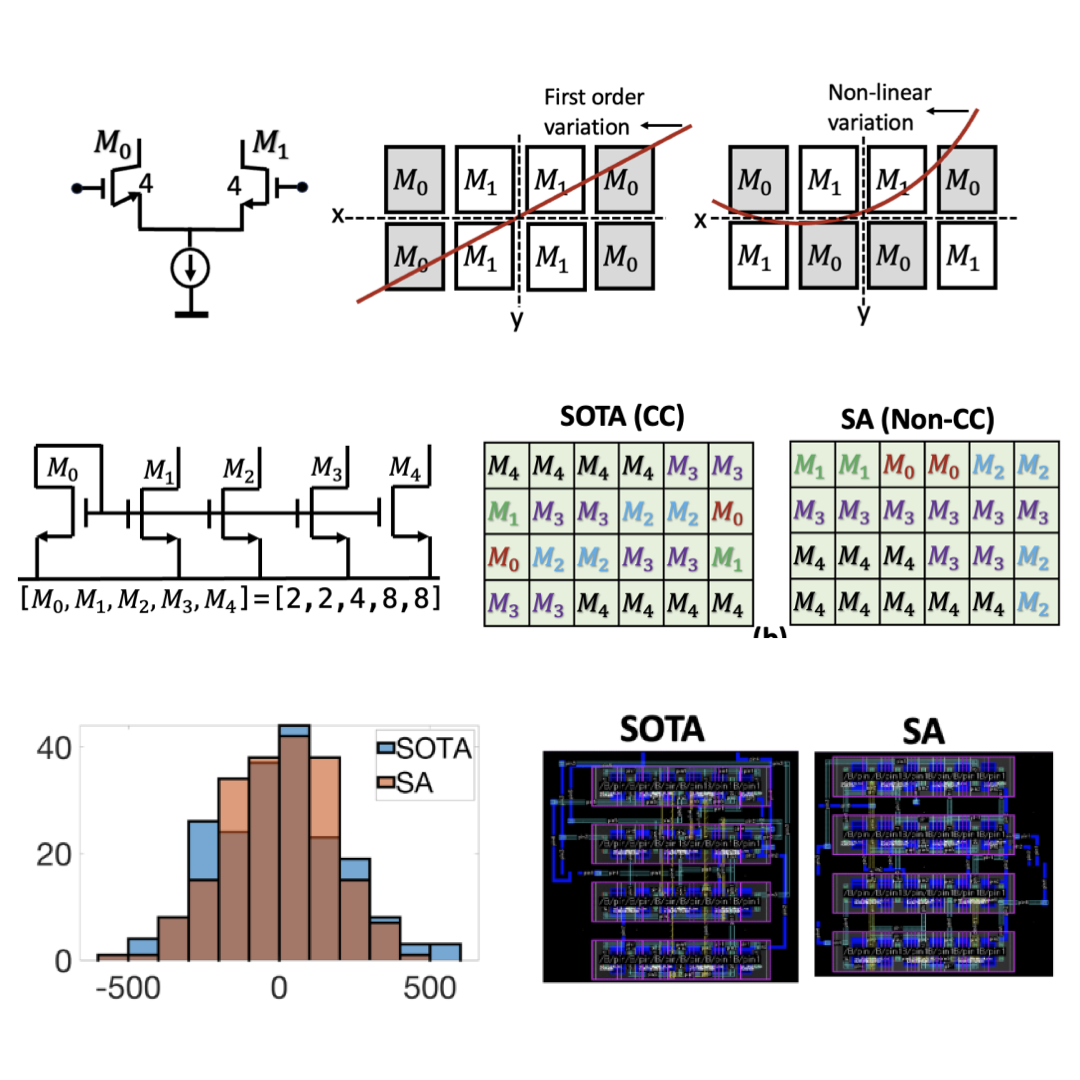

Analog Transistor Placement Optimization Considering Nonlinear Spatial Variations

Supriyo Maji, Sungyoung Lee, David Z. Pan

Design, Automation & Test in Europe Conference & Exhibition (DATE) 2024

This work proposes a simulated annealing-based transistor placement method to mitigate nonlinear spatial variations in analog circuits. It outperforms state-of-the-art techniques while handling key layout constraints and offering better control over optimization objectives.

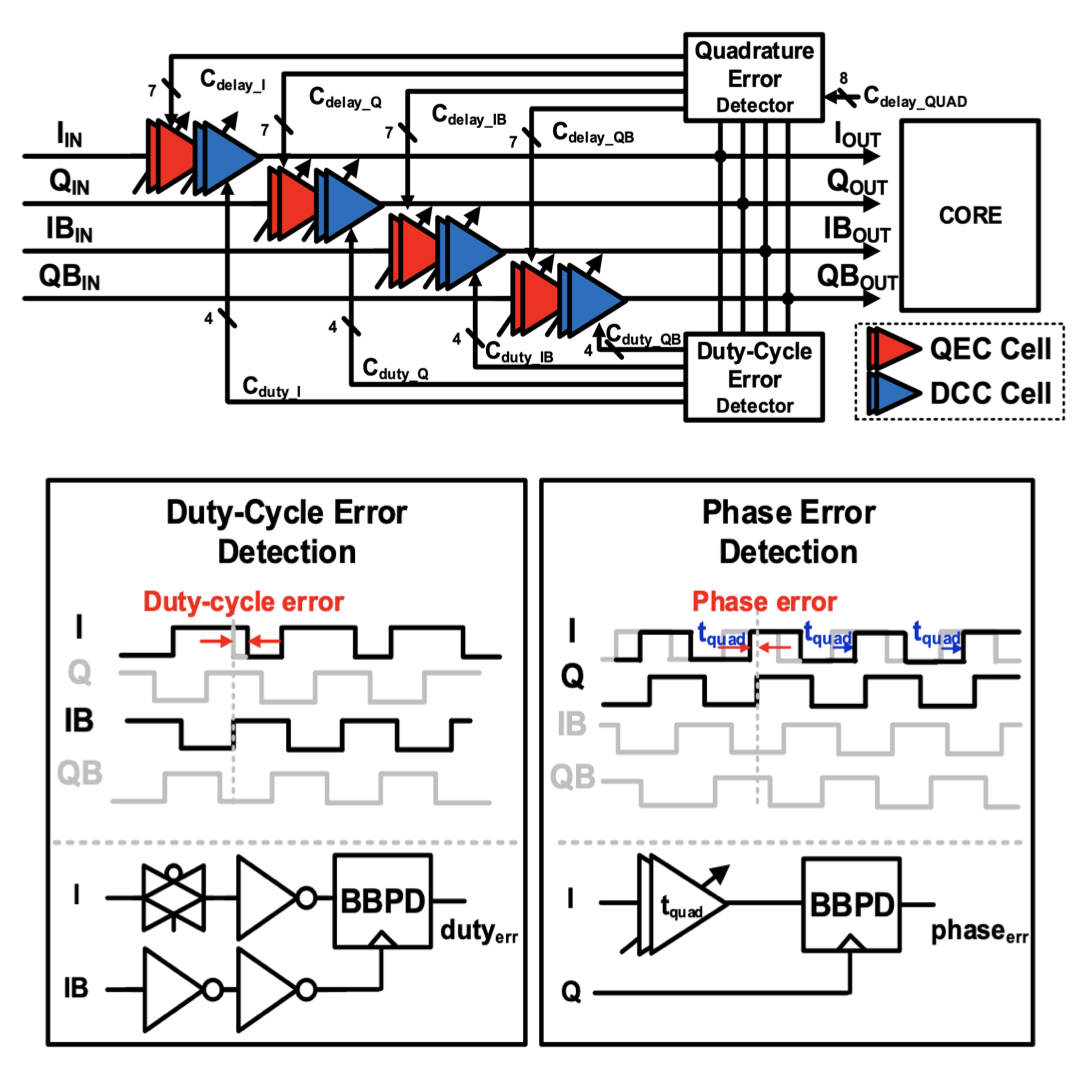

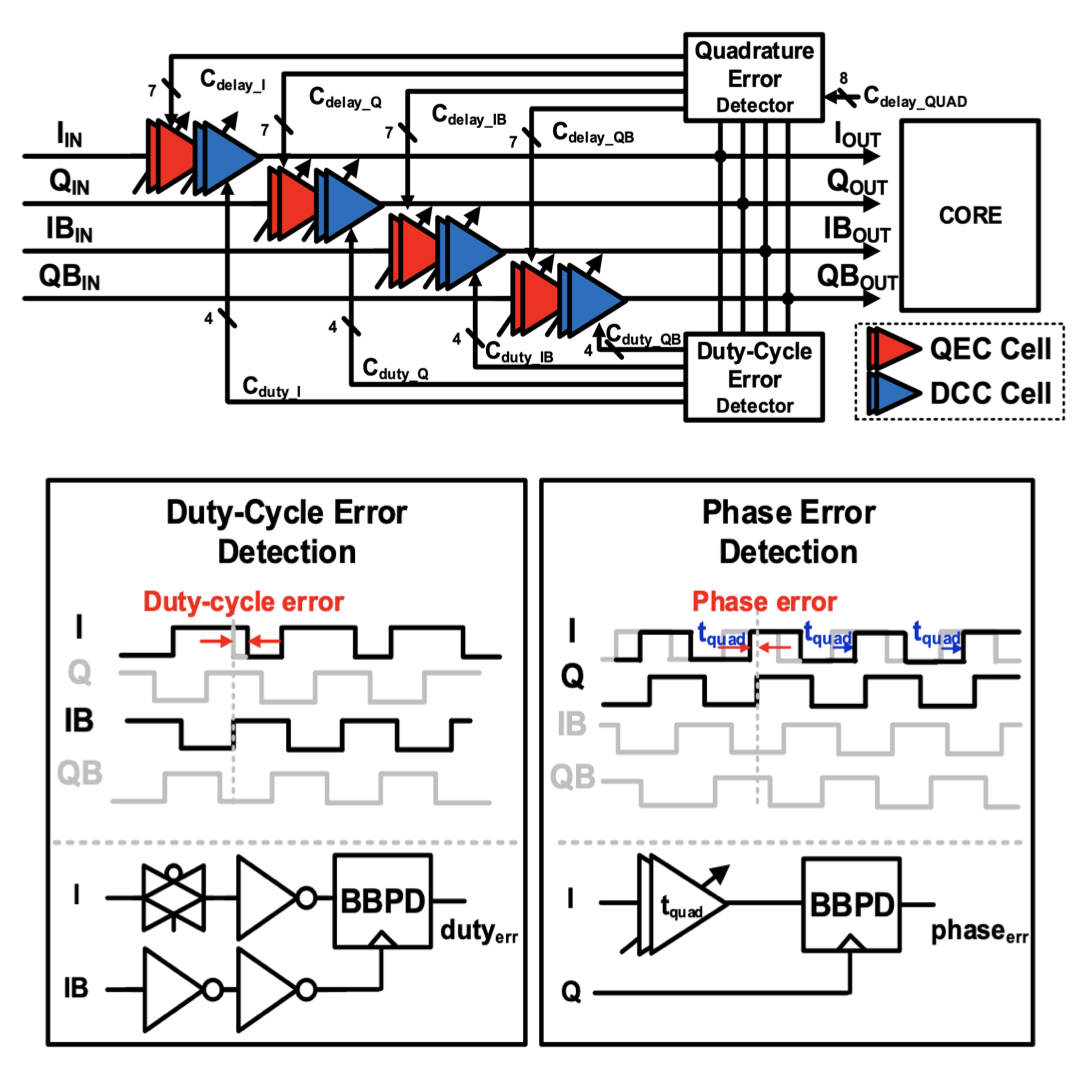

A 10-to-12-GHz Dual Loop Quadrature Clock Corrector in 28-nm CMOS Technology

Jung-Woo Sull, Sungyoung Lee, Deog-Kyoon Jeong

37th International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC) 2022

This paper presents a 10–12 GHz dual-loop quadrature clock corrector using a digital DLL with concurrent QEC and DCC loops for stability. Implemented in 28-nm CMOS, it achieves 0.6 ps phase inaccuracy and 0.7% duty cycle error while consuming 16.5 mW at 12 GHz.